台湾大学研究团队提出了一个统一模型,用来解释通道厚度、缺陷、界面质量和表面粗糙度如何共同决定超薄氧化物晶体管的电学行为。相关成果发表在《Small Structures》期刊上,为构建低漏电、常关型器件提供了可操作的设计准则,特别适用于未来三维芯片堆叠中的低温工艺晶体管。

更完善的模型支撑更优的超薄器件

随着半导体技术向三维集成演进,新一代晶体管必须能够直接堆叠在既有电路之上,同时避免对下层结构造成热或电学损伤。这对器件提出了多重要求:制程温度要足够低、通道要极薄、功耗要极小,并且开关特性要稳定可靠。

氧化物半导体被视为满足这些条件的有力候选,但当通道厚度缩减到几纳米时,其行为往往变得难以预测。缺陷密度的微小变化、界面质量的轻微差异,甚至表面粗糙度的细微起伏,都可能显著影响漏电流、阈值电压、载流子迁移率以及长期稳定性。

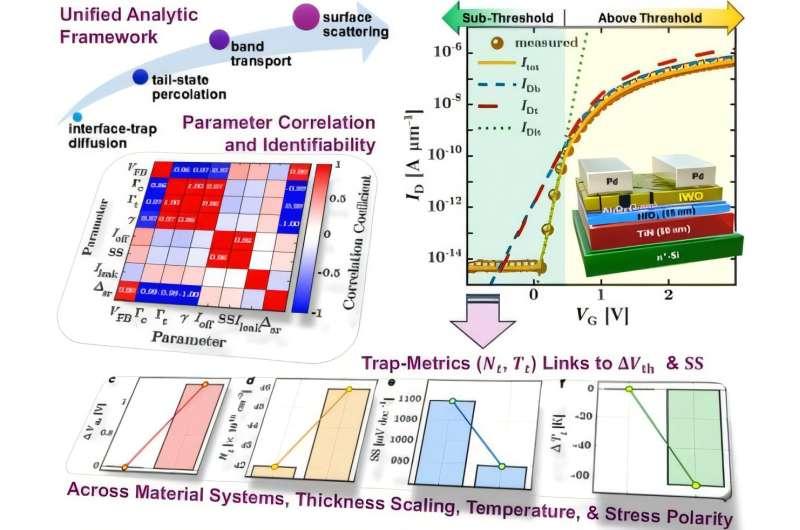

台湾大学此次工作正是针对这种不确定性提出系统解决方案。研究人员并未只停留在单纯的器件性能对比,而是构建了一个统一的解析模型,覆盖基于氧化铟的超薄晶体管在整个开关区间内的工作机理。该模型将通常分开处理的多种效应纳入同一框架:包括常规能带传输、电荷陷阱相关电流、介电层界面缺陷辅助电流,以及在通道接近原子级厚度时由表面粗糙度引起的迁移率退化。

厚度、陷阱、界面与粗糙度的一体化描述

为验证这一框架,团队系统研究了以氧化铟和钨掺杂氧化铟(IWO)为通道材料的晶体管,通道厚度范围约为 2–13 纳米。实验结果表明,在极薄通道条件下,纯氧化铟器件变得难以精确控制,而 IWO 器件则表现出更好的可控性和稳定性。

更关键的进展不在于简单指出哪种材料更优,而在于模型能够定量再现测得的电流–电压特性,并进一步揭示两种材料行为差异背后的物理原因。

借助该模型,研究人员提取出两个尤为关键的参数:陷阱态的数量以及其能量分布的宽度。这些与陷阱相关的量直接关联到工程上关注的核心指标,例如关断态漏电、亚阈值摆幅、阈值电压漂移以及迁移率变化。模型中还引入了一个同时依赖通道厚度和栅极偏压的迁移率项,用来描述当电子被压向栅介电层时,粗糙度散射在超薄通道中如何变得更加显著。

从数据拟合走向设计工具

研究显示,钨掺杂通过两个主要途径改善氧化铟材料的器件表现:一方面,它抑制了多余载流子,降低了关断态漏电,使实现常关型工作更加容易;另一方面,它减轻了材料无序度,改善了与栅介电层的界面质量,从而在通道厚度仅有 2–3 纳米时仍能维持较好的迁移率和亚阈值特性。量子力学计算结果支持这一解释,表明 IWO 与介电层界面更加平滑且具有更高的相干性。

该统一框架还被用来分析电应力下的可靠性行为。在较厚通道器件中,电应力主要改变陷阱能级分布的宽度,有时甚至会在一定程度上改善开关特性;而在超薄器件中,界面效应占主导,应力更容易激活界面陷阱,导致工作电压发生漂移。通过在同一物理图景下描述这两类现象,模型为偏置稳定性测试提供了更清晰的解释路径,而不再只是经验性地罗列结果。

这项工作的更深层意义在于,将实验测量转化为可预测的设计方法。工程师不必完全依赖反复试验,而是可以利用该框架定量评估通道厚度、掺杂策略、无序程度和界面质量之间的权衡关系,以达到目标器件指标。对于要求制程温度低于 400°C 的后端工艺电子而言,这种基于物理的设计工具尤为关键,因为它同时要满足严格的漏电、开关速度和长期稳定性约束。

面向三维集成电子的实用指导

总体而言,该研究表明,超薄氧化物晶体管的设计不能将厚度、材料选择或缺陷密度割裂开来单独优化,这些因素在器件尺度下是强耦合的。所提出的统一模型正是从这一点出发,提供了一个基于物理机制的描述方法,既能解释现有器件的行为,也能为未来堆叠芯片技术中更优器件结构的设计提供定量指导。

“这项工作的主要贡献是建立了一个统一模型,能够准确刻画超薄氧化物晶体管的工作特性,并帮助设计人员识别出更具潜力的材料组合和通道厚度选择。”台湾大学先进技术研究所半导体器件、材料与异质集成教授、共同通讯作者李敏宏博士表示。

“我们的目标是从零散的器件演示迈向一个可预测的设计框架,用于开发适用于未来三维集成电子的、在低温工艺下依然可靠的晶体管。”