量子计算机依赖量子力学效应处理信息。相关研究指出,为支持复杂任务运行,系统需要更快、能耗更低的存储组件。由超导体构成的超导存储器被视为潜在方案之一:超导体在冷却至临界温度以下时电阻为零。

不过,研究人员同时指出,尽管超导存储器在速度与能耗方面具备潜力,现有不少方案仍面临易出错、难以扩展到多存储单元大型系统等问题。

麻省理工学院(MIT)研究人员近日在《Nature Electronics》发表论文,介绍一种基于纳米线的可扩展超导存储器设计。论文作者Owen Medeiros、Matteo Castellani及其同事表示,可扩展的超导存储器对低能耗超导计算机与容错量子计算机的发展具有重要意义。

研究团队报告了一种面向行列操作的4×4超导纳米线存储阵列,功能密度达到2.6 Mbit/cm²。作者称,相比以往多种基于超导纳米线的存储器,该阵列实现了更低的错误率。

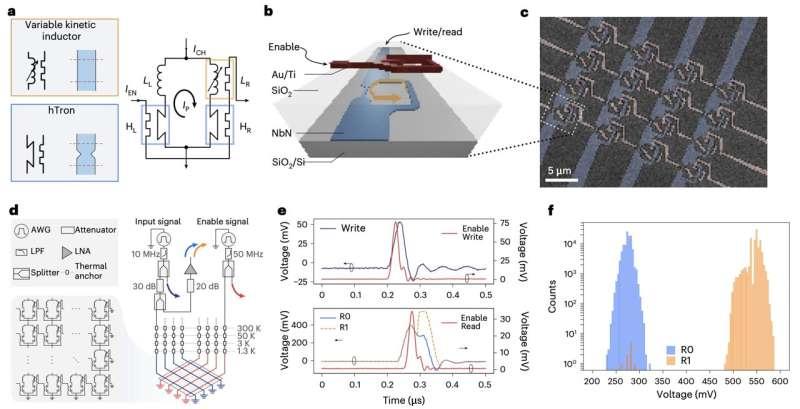

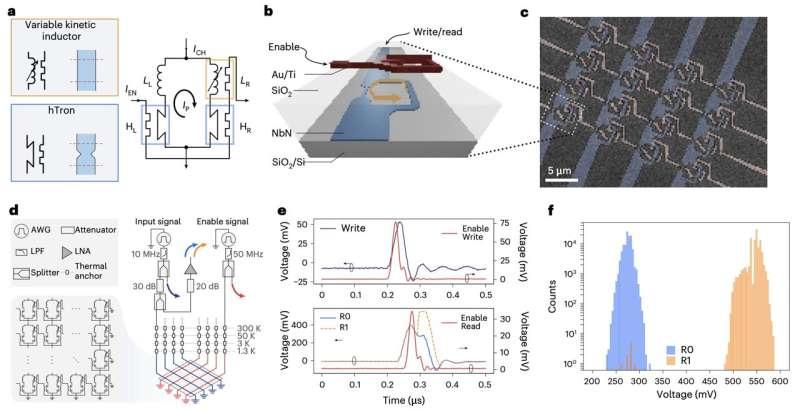

在结构上,每个存储单元由一个超导纳米线环路构成,并配备两个开关与一个动能电感器。研究人员介绍,两个超导开关的电阻会随温度变化;动能电感器用于抵抗电流变化,使电流按可预测模式流动,从而支持存储器稳定运行。

论文称,该阵列在1.3 K条件下运行,实现并表征了多磁通量量子态存储与破坏性读出。研究团队通过优化写入与读取的脉冲序列,以降低位错误率并扩大操作裕度。

在读写机制方面,研究人员通过精确时序的电脉冲对特定单元进行写入与读取。电脉冲会短暂加热其中一个纳米线开关,提高其电阻并向环路注入磁通量;磁通量用于编码数据值(0或1)。脉冲结束后,纳米线冷却回超导状态,信息对应的磁通量被困在纳米线环路中。

测试结果显示,该存储阵列在约10万次操作中仅出现1次错误。作者在论文中写道,其实现的最低位错误率为10⁻⁵,并使用电路级仿真分析存储单元动态、性能极限以及在不同脉冲幅度下的稳定性。

研究人员表示,这一结果有望推动超导存储系统向更可靠的实际应用迈进,后续设计仍可进一步改进并扩展,以构建更高性能的存储系统。

© 2026 Science X Network