从智能手机到大规模人工智能服务器,现代社会的大部分数字信息都依赖 NAND 闪存来存储。针对下一代半导体在有限空间内继续提升存储密度的难题,KAIST 研究团队提出了一项新技术,有望成为实现超大容量存储器的关键支撑。

由 KAIST 电气工程系赵炳镇教授领衔的团队,在比人类头发还要细得多的超薄半导体层上引入新材料,构建出一种“智能栅极”结构。该结构能够根据不同工作条件选择性调控电子运动,从而突破当前 3D V‑NAND 存储器在缩小尺寸时面临的物理极限。

这项研究由电气工程专业集成硕博课程学生姜大贤担任第一作者,成果已于 12 月 9 日在半导体领域顶级会议之一——IEEE 国际电子器件会议(IEDM)上发表,并引起国际学术界和产业界的广泛关注。

研究的核心在于引入一种名为氧氮化硼(BON)的新型材料,用以解决长期困扰业界的两大问题:在数据写入和擦除过程中速度下降,以及器件可靠性不足。

在半导体存储器中,隧穿层是一层极薄的绝缘层,是电子进出存储单元的必经通道,其设计一直存在性能与可靠性难以兼顾的矛盾。

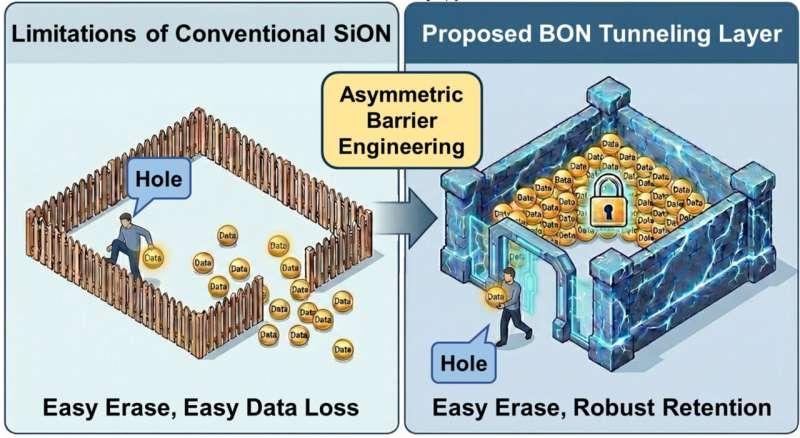

采用传统材料时,这种权衡尤为突出。当前广泛使用的氧氮化硅(SiON)就是典型例子:如果加宽隧穿路径以提升擦除速度,会导致数据泄漏增加;若缩窄路径以抑制泄漏,又会显著拖慢擦除速度。这种两难局面成为实现下一代五级单元(PLC)技术的主要障碍。

PLC 技术通过区分 32 个不同的电压状态,使每个存储单元可以存储 5 位数据,从而在相同物理面积下实现更高的数据密度,对隧穿层的性能和稳定性提出了极高要求。

为打破这一限制,研究团队在隧穿层中引入了超越传统硅基体系的全新材料 BON。该材料展现出独特的物理特性:对不同类型载流子呈现不同的能垒高度。

基于这一特性,团队设计出非对称能垒结构,使得在擦除操作中所需的空穴(带正电的载流子)可以顺利通过,而代表存储信息的电子则被有效阻挡,难以泄漏。

所谓非对称能垒,是指不同载流子在通过材料时所需克服的能量高低不同。借助这种结构,可以在擦除过程中实现高效的载流子传输,同时又能可靠地防止数据丢失。可以将其类比为半导体层面的“智能栅门”:允许特定载流子轻松进入或通过,但对不希望通过的载流子形成严密阻挡。

实验结果表明,采用 BON 作为隧穿层的器件,其擦除速度相比传统技术提升了 23 倍;即便在经历数万次写入/擦除循环后,性能退化仍然极小,显示出出色的耐久性。

更为关键的是,在要求极高的 PLC 操作条件下——需要精确区分 32 个电压等级——研究人员仍然实现了器件间数据分布控制能力提升超过三倍的表现。

学界和产业界普遍认为,这一成果不仅停留在实验室验证层面,而是已经达到了可以直接导入实际半导体制造工艺的成熟度。

赵炳镇教授表示:“本研究提出了一项可直接应用于下一代超大容量存储器生产的创新技术,将大幅提升韩国在全球半导体产业中的技术竞争力和领先优势。”

该工作在第 32 届三星人文科技论文奖中获得大学组一等奖(总冠军),在以人工智能相关研究为主流的竞赛中,以传统半导体器件方向的成果脱颖而出,具有标志性意义。