近二十年来,二维(2D)半导体因有望实现更小、更快、更节能的晶体管而受到持续关注,被视为硅晶体管的补充或潜在替代方案。为简化制备与测试流程,相关研究中广泛采用一种便于在单片硅基底上完成器件构建的测试架构。

杜克大学电气与计算机工程系研究团队近日指出,上述常用测试方法可能在不易察觉的情况下抬高二维晶体管的实验室“纸面性能”,且这种提升难以直接转化为可用于商业技术的器件表现。相关论文于2月17日发表在《ACS Nano》,研究来自埃伦·富兰克林(Aaron Franklin)教授实验室;富兰克林为该系埃德蒙·T·普拉特二世杰出教授。

富兰克林在研究中表示,许多被报告为高性能的二维晶体管采用了与商业技术不兼容的器件设计;该设计会改变晶体管的工作方式,从而显著放大测得性能,若不加区分,将难以对材料在未来晶体管技术中的潜在表现进行公平比较。

晶体管是计算系统的基础器件,通过快速开关电流实现数字电路中的“1”和“0”。在提升处理性能的路径上,器件需要在尺寸、速度与能效等方面持续改进。硅长期是主流半导体材料,但随着器件结构不断变薄,相关技术逐步逼近物理极限,促使研究人员探索在原子级厚度下仍可工作的二维材料。

背门控测试与“接触门控”

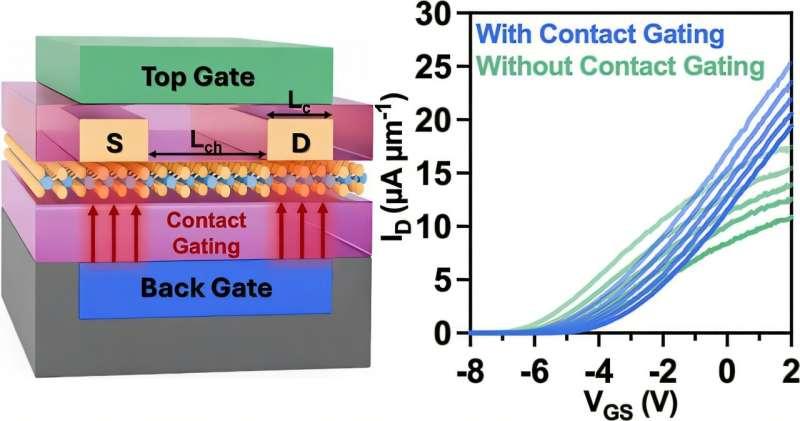

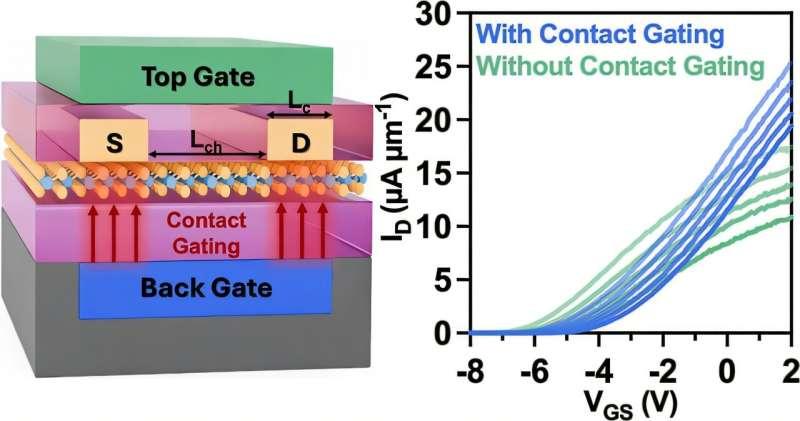

研究团队将焦点放在二维晶体管常用的“背门控”测试架构上。在该架构中,超薄二维半导体(如二硫化钼,MoS₂)位于两个金属接触电极之间,电流通过半导体通道传导;器件的开关由硅基底充当的门极电压来调制。

论文指出,背门控不仅会调制二维半导体通道本身,也会影响金属接触下方的半导体区域,从而产生“接触门控”现象。该效应可通过门控降低接触电阻,进而放大晶体管的测量性能。研究同时强调,背门控架构虽便于实验室基础测试,但由于速度限制与电流泄漏等因素,难以用于实际器件技术。

构建对照器件并量化影响

为直接评估接触门控对性能的贡献,富兰克林实验室博士生维多利亚·拉维尔(Victoria Ravel)用一年时间制备了新的器件架构。团队构建了一种对称双门晶体管,使门极、电极与材料在同一二维半导体通道的上下方对称分布,并通过采用背门控或顶门控进行控制,实现仅在“是否存在接触门控”这一因素上不同的对照比较。

拉维尔在研究中提到,器件制备过程中存在不确定性,在极小尺寸下加工会受到物理极限约束,操作难度显著增加。

实验结果显示,在较大尺寸器件中,接触门控可使性能约提升一倍;随着器件缩小到更接近未来技术需求的尺度,该效应进一步增强。在通道长度50纳米、接触长度30纳米的条件下,接触门控带来的性能提升最高可达六倍。

研究团队解释,器件尺寸越小,接触部分对整体性能的主导作用越强,任何改变接触行为的机制都会变得更关键。鉴于过去大量二维晶体管研究采用背门控架构,团队认为上述发现对相关实验结果的解读具有广泛影响。

后续研究方向

团队表示,下一步计划继续缩小器件尺寸,将接触长度降至15纳米,并评估替代接触金属以降低接触电阻。研究的更广泛目标是为二维半导体在未来晶体管技术中的集成建立更清晰的器件设计规则,并在测量与架构选择上更准确地区分可比性能。

富兰克林表示,若二维材料未来要取代硅通道,需要正视器件架构对测量结果的影响;相关工作旨在为此奠定基础。